## EE 435

## Lecture 4

#### Fully Differential Single-Stage Amplifier Design

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Overall Transfer Characteristics

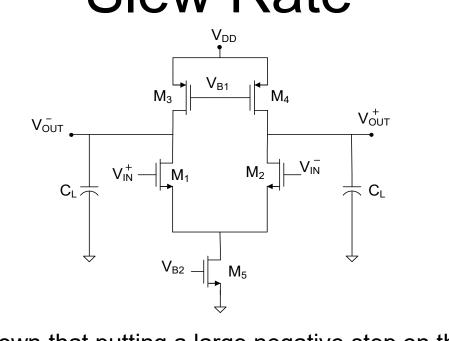

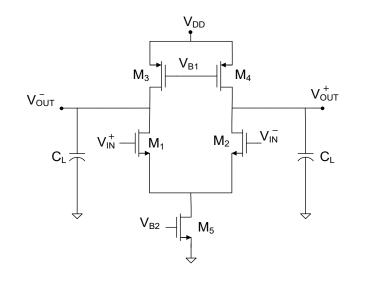

Design of 5T Op Amp Slew Rate

#### **Review from last lecture:** Where we are at:

## Basic Op Amp Design

Fundamental Amplifier Design Issues

- Single-Stage Low Gain Op Amps

- Single-Stage High Gain Op Amps

- Two-Stage Op Amp

- Other Basic Gain Enhancement Approaches

## Review from last lecture: Where we are at:

## Single-Stage Low-Gain Op Amps

Single-ended input

Differential Input

(Symbol does not distinguish between different amplifier types)

## Differential Input Low Gain Op Amps

Will Next Show That:

Differential input op amps can be readily obtained from single-ended op amps

Performance characteristics of differential op amps can be directly determined from those of the single-ended counterparts

## **Counterpart Networks**

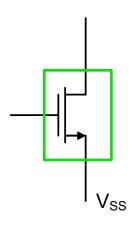

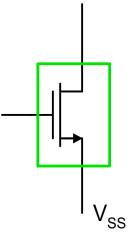

Definition: The counterpart network of a network is obtained by replacing all n-channel devices with p-channel devices, replacing all p-channel devices with n-channel devices, replacing V<sub>SS</sub> biases with V<sub>DD</sub> biases, and replacing all V<sub>DD</sub> biases with V<sub>SS</sub> biases.

## **Counterpart Networks**

Theorem: The parametric expressions for all small-signal characteristics, such as voltage gain, output impedance, and transconductance of a network and its counterpart network are the same.

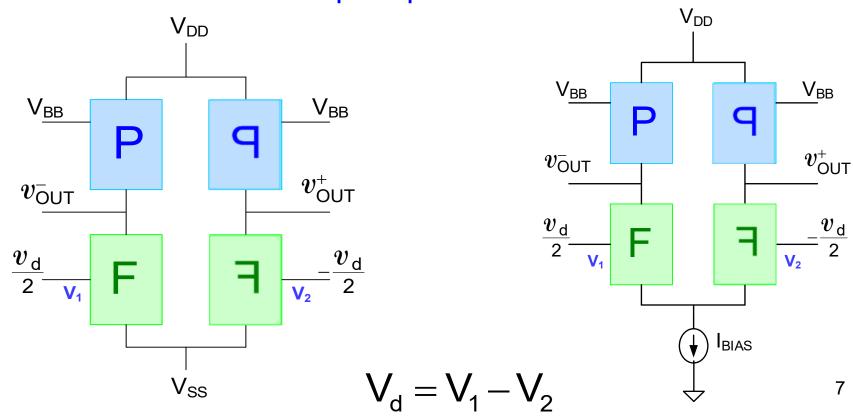

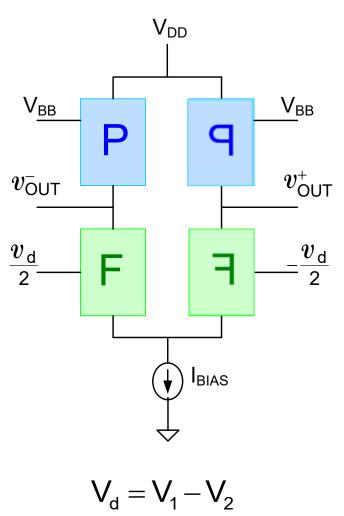

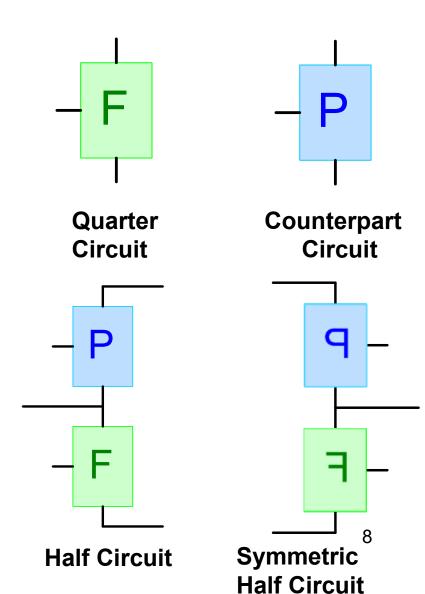

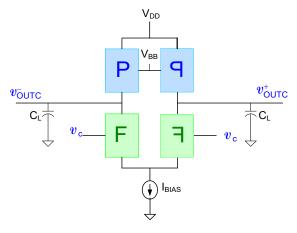

# Synthesis of fully-differential op amps from symmetric networks and counterpart networks

Theorem: If F is any network with a single input and P is its counterpart network, then the following circuits are fully differential circuits --- "op amps".

# Synthesis of fully-differential op amps from symmetric networks and counterpart networks

## **Terminology**

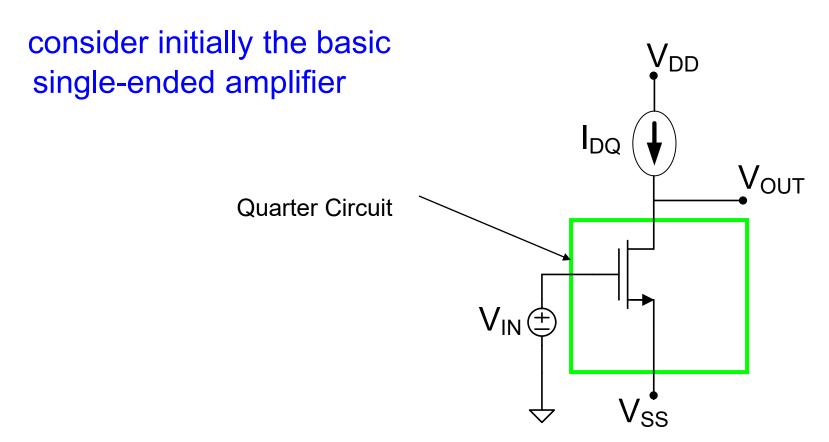

# Applications of Quarter-Circuit Concept to Op Amp Design

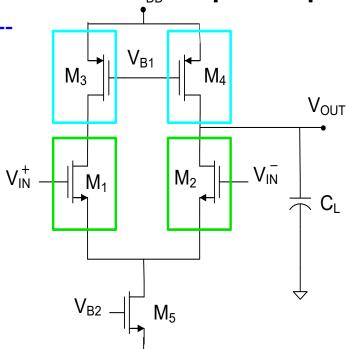

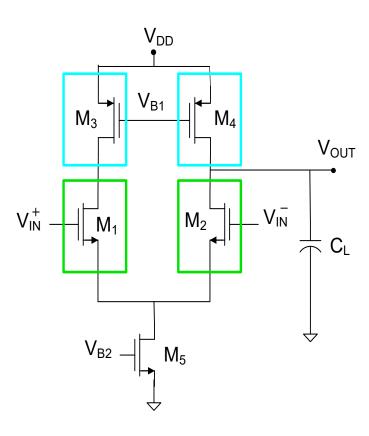

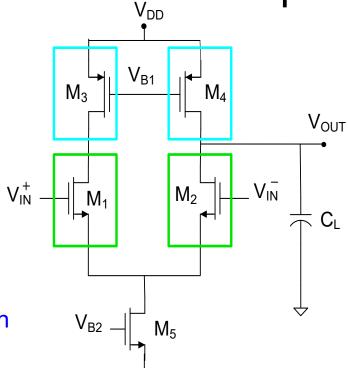

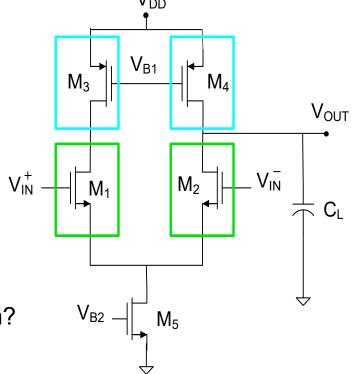

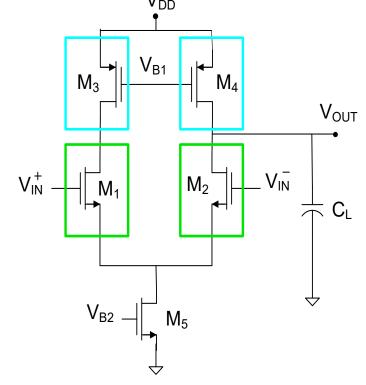

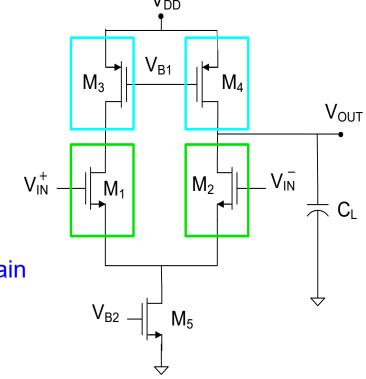

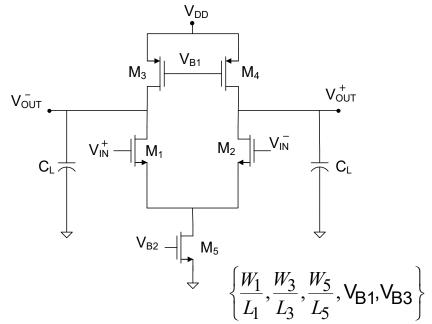

#### Review from last lecture: Single-stage low-gain differential op amp

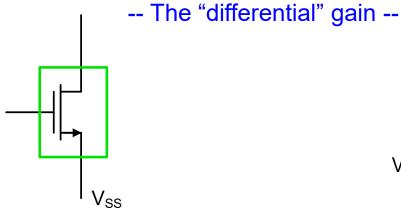

#### **Quarter Circuit**

Single-Ended Output: Differential Input Gain

$$A(s) = \frac{v_{OUT}}{v_{d}} = \frac{-\frac{g_{m1}}{2}}{sC_{L} + g_{o1} + g_{o3}}$$

$$A_{V0} = \frac{-g_{m1}}{2(g_{o1} + g_{o3})}$$

$$BW = \frac{g_{o1} + g_{o3}}{C_{i}}$$

$$GB = \frac{g_{m1}}{2C}$$

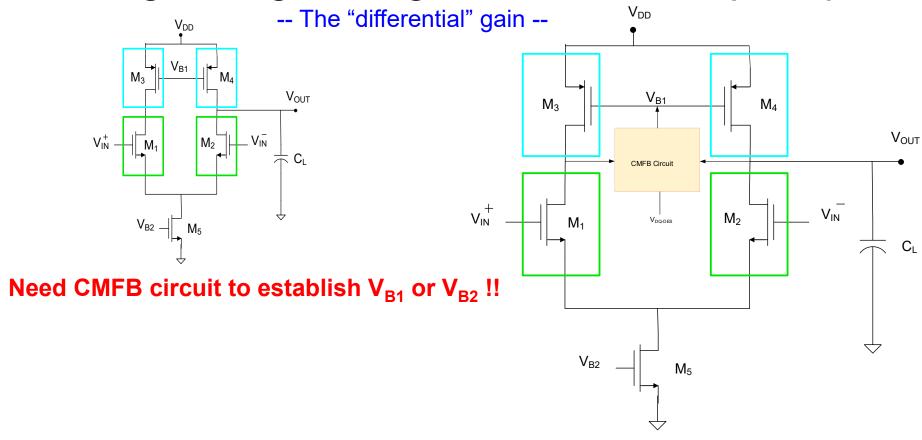

### Circuit is Very Sensitive to $V_{\rm B1}$ and $V_{\rm B2}$ !!

- Have synthesized fully differential op amp from quarter circuit!

- Have obtained analysis of fully differential op amp directly from quarter circuit!

- Still need to determine what happens if input is not differential!

10

Have almost obtained op amp characteristics by inspection from quarter circuit !!

## Single-stage low-gain differential op amp

- CMFB circuit determines average value of the drain voltages

- Compares the average to the desired quiescent drain voltages

- Established a feedback signal V<sub>B1</sub> to set the right Q-point

- Shown for V<sub>B1</sub> but could alternately be applied to V<sub>B2</sub>

- Fully Differential Single-Stage Amplifier

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

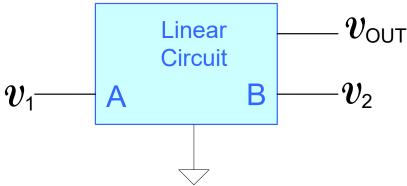

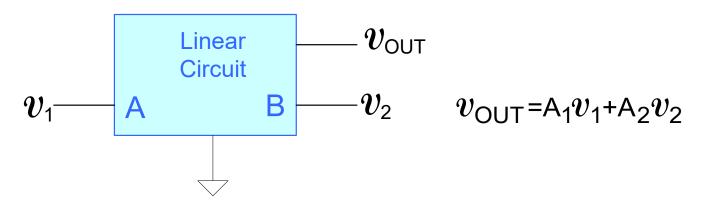

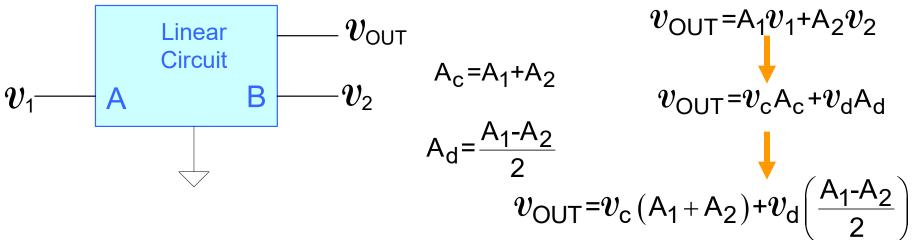

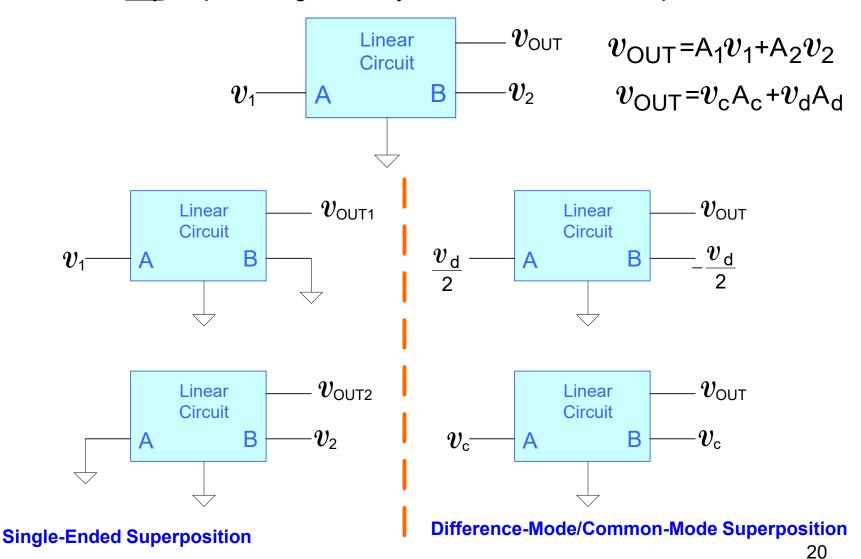

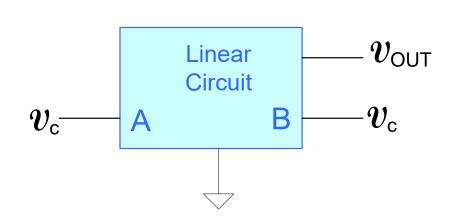

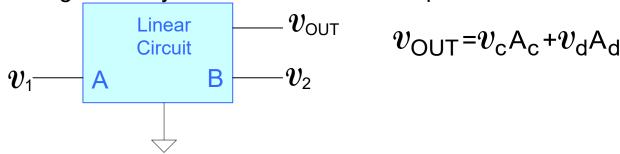

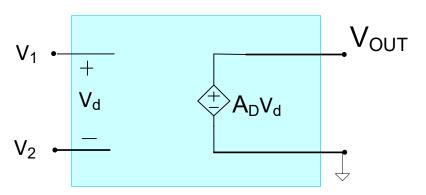

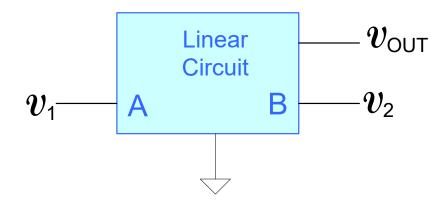

Consider <u>an</u> output voltage for any linear circuit with two inputs (i.e. need not be symmetric)

By superposition

$$v_{\mathsf{OUT}}$$

=A $_1v_1$ +A $_2v_2$

where  $A_1$  and  $A_2$  are the gains (transfer functions) from inputs 1 and 2 to the output respectively

Define the common-mode and difference-mode inputs by

$$v_{c} = \frac{v_{1} + v_{2}}{2}$$

$v_{d} = v_{1} - v_{2}$

These two equations can be solved for  $v_{\scriptscriptstyle 1}$  and  $v_{\scriptscriptstyle 2}$  to obtain

$$v_1$$

= $v_c$ + $\frac{v_d}{2}$

$$v_2$$

= $v_{\rm c}$ - $\frac{v_{\rm d}}{2}$

Consider an output voltage for any linear circuit with two inputs

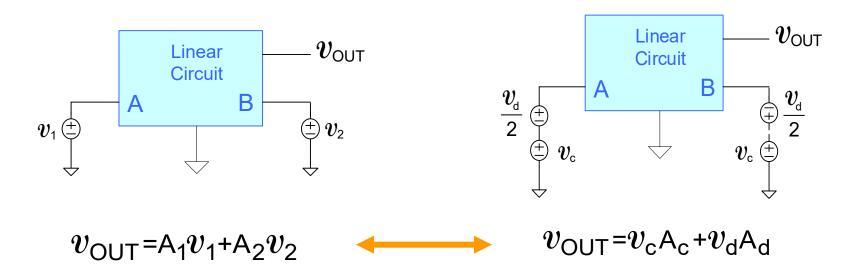

Substituting into the expression for  $v_{\scriptscriptstyle \mathsf{OUT}}$ , we obtain

$$v_{ ext{OUT}}$$

=A $_1$  $\left(v_{ ext{c}}+rac{v_{ ext{d}}}{2}

ight)$ +A $_2$  $\left(v_{ ext{c}}-rac{v_{ ext{d}}}{2}

ight)$

Rearranging terms we obtain

$$v_{\text{OUT}} = v_{\text{c}} (A_1 + A_2) + v_{\text{d}} \left(\frac{A_1 - A_2}{2}\right)$$

If we define A<sub>c</sub> and A<sub>d</sub> by

$$A_c = A_1 + A_2$$

$A_d = \frac{A_1 - A_2}{2}$

Can express  $v_{\scriptscriptstyle extsf{OUT}}$  as

$$v_{\mathsf{OUT}}$$

= $v_{\mathsf{c}}\mathsf{A}_{\mathsf{c}}$ + $v_{\mathsf{d}}\mathsf{A}_{\mathsf{d}}$

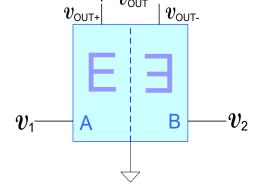

Depiction of singe-ended inputs and common/difference mode inputs

#### Alternate Equivalent Represntations

- Applicable to any linear circuit with two inputs and a single output

- Op amps often have symmetry and this symmetry further simplifies analysis

Consider any output voltage for any linear circuit with two inputs

Implication: Can solve any linear two-input circuit by applying superposition with  $v_{\rm 1}$  and  $v_{\rm 2}$  as inputs or with  $v_{\rm c}$  and  $v_{\rm d}$  as inputs. This can be summarized in the following theorem:

Theorem 1: The output for any linear network can be expressed equivalently as  $v_{\rm OUT}$ =A<sub>1</sub> $v_{\rm 1}$ +A<sub>2</sub> $v_{\rm 2}$  or as  $v_{\rm OUT}$ = $v_{\rm c}$ A<sub>c</sub>+ $v_{\rm d}$ A<sub>d</sub> Superposition can be applied to either  $v_{\rm 1}$  and  $v_{\rm 2}$  to obtain A<sub>1</sub> and A<sub>2</sub> or to  $v_{\rm c}$  and  $v_{\rm d}$  to obtain A<sub>c</sub> and A<sub>d</sub>

Observation: In a circuit with  $A_2$ = -  $A_1$ ,  $A_C$ =0 we obtain  $v_{\rm OUT}$ = $v_{\rm d}$ A<sub>d</sub>

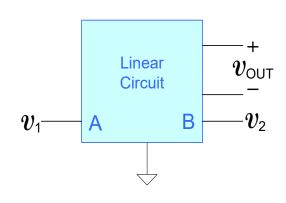

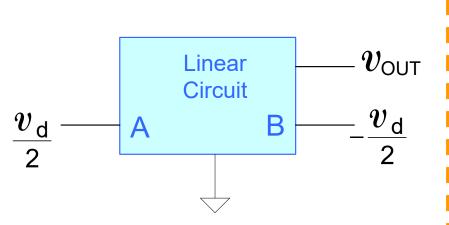

**Extension** to differential outputs and symmetric circuits  $+v_{ ext{out}}$

**Differential Output**

Symmetric Circuit with Symmetric Differential Output

Observation: In a symmetric circuit with a symmetric differential output,  $A_{\rm C}$ =0 so can be shown that  $v_{\rm OUT}$ = $v_{\rm d}$ A<sub>d</sub> This is summarized in the theorem:

Theorem 2: The symmetric differential output voltage for any symmetric linear network excited at symmetric nodes can be expressed as

$$v_{\mathsf{OUT}}$$

=A $_{\mathsf{d}}v_{\mathsf{d}}$

where  $A_d$  is the differential voltage gain and the voltage  $v_d$  =  $v_1$  -  $v_2$

## Symmetric Circuit with Symmetric Differential Output

Theorem 2: The symmetric differential output voltage for any symmetric linear network excited at symmetric nodes can be expressed as

$$v_{\mathsf{OUT}}$$

=A $_{\mathsf{d}}v_{\mathsf{d}}$

where  $A_d$  is the differential voltage gain and the voltage  $v_d$  =  $v_1$  -  $v_2$

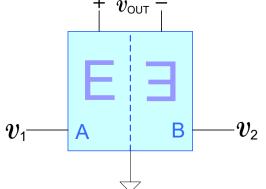

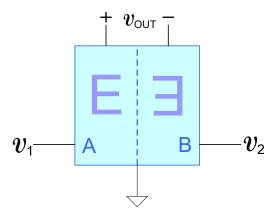

## **Proof of Theorem 2 for Symmetric Circuit with Symmetric Differential Output:**

By superposition, the single-ended outputs can be expressed as

$$v_{\mathsf{OUT}}$$

+ =  $\mathsf{T}_{\mathsf{OPA}}v_{\mathsf{1}}$  +  $\mathsf{T}_{\mathsf{OPB}}v_{\mathsf{2}}$

$$v_{\mathsf{OUT}}$$

- =  $\mathsf{T}_{\mathsf{ONA}}v_{\mathsf{1}}$  +  $\mathsf{T}_{\mathsf{ONB}}v_{\mathsf{2}}$

where  $T_{0PA}$ ,  $T_{0PB}$ ,  $T_{0NA}$  and  $T_{0NB}$  are the transfer functions from the A and B inputs to the single-ended + and - outputs

taking the difference of these two equations we obtain

$$v_{\mathsf{OUT}}$$

=  $v_{\mathsf{OUT+}}$  -  $v_{\mathsf{OUT-}}$  =  $(\mathsf{T}_{\mathsf{OPA}}\mathsf{-}\mathsf{T}_{\mathsf{ONA}})v_{\mathsf{1}} + (\mathsf{T}_{\mathsf{OPB}}\mathsf{-}\mathsf{T}_{\mathsf{ONB}})v_{\mathsf{2}}$

by symmetry, we have

$$T_{OPA} = T_{ONB}$$

and  $T_{ONA} = T_{OPB}$

thus can express  $V_{OUT}$  as

$$v_{\text{OUT}} = (T_{\text{OPA}} - T_{\text{ONA}})(v_1 - v_2)$$

or as

$$v_{\mathsf{OUT}}$$

=A $_{\mathsf{d}}v_{\mathsf{d}}$

where

$$A_d$$

=  $T_{OPA}$ - $T_{ONA}$  and where  $v_d$  =  $v_1$  -  $v_2$

Consider any output voltage for any linear circuit with two inputs

Consider an output voltage for any linear circuit with two inputs

- Difference-Mode/Common-Mode Superposition is almost exclusively used for characterizing Amplifiers that are designed to have a large differential gain and a small common-mode gain

- Analysis to this point has been focused only on the circuit on the left

Note: Previous analysis was correct, just did not address whether the circuit had any common mode gain.

Consider an output voltage for any linear circuit with two inputs

Does Conventional Wisdom Address the Common Mode Gain Issue?

#### Does Conventional Wisdom Address the Common Mode Gain Issue?

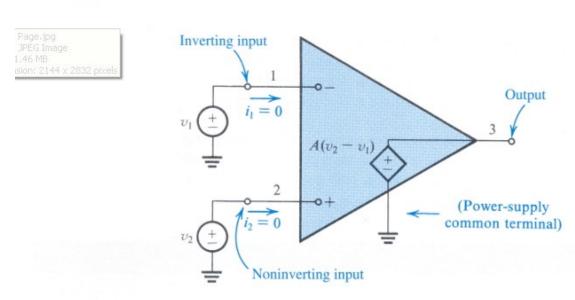

**CHAPTER 2** OPERATIONAL AMPLIFIERS Inverting input Output  $i_1 = 0$  $A(v_2)$ (Power-supply  $i_2 = 0$ common terminal)

FIGURE 2.3 Equivalent circuit of the ideal op amp.

Noninverting input

23

# Does Conventional Wisdom Address the Common Mode Gain Issue?

66 CHAPTER 2 OPERATIONAL AMPLIFIERS

FIGURE 2.3 Equivalent circuit of the ideal op amp.

#### TABLE 2.1 Characteristics of the Ideal Op Amp

- 1. Infinite input impedance

- 2. Zero output impedance

- 3. Zero common-mode gain or, equivalently, infinite common-mode rejection

- 4. Infinite open-loop gain A

- 5. Infinite bandwidth

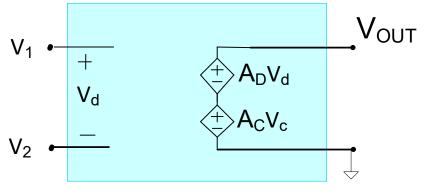

### How is Common-Mode Gain Modeled?

If Op Amp is a Voltage Amplifier with infinite input impedance, zero output impedance, and one terminal of the output is grounded

Ideal Differential Voltage Amplifier

$$V_d = V_1 - V_2$$

Ideal Voltage Amplifier

$$V_d = V_1 - V_2$$

$V_c = \frac{V_1 + V_2}{2}$

- Fully Differential Single-Stage Amplifier

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

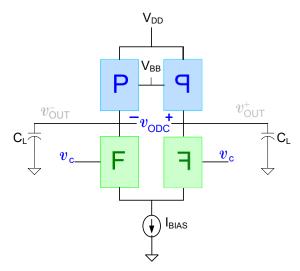

Single-Ended Outputs

Tail-Current Bias

Differential Output Tail Current Bias

Single-Ended Outputs

Tail-Voltage Bias

Differential Output Tail Voltage Bias

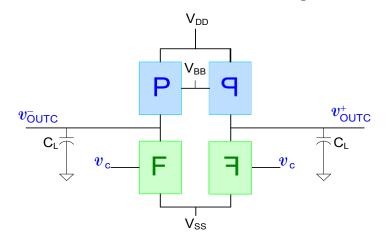

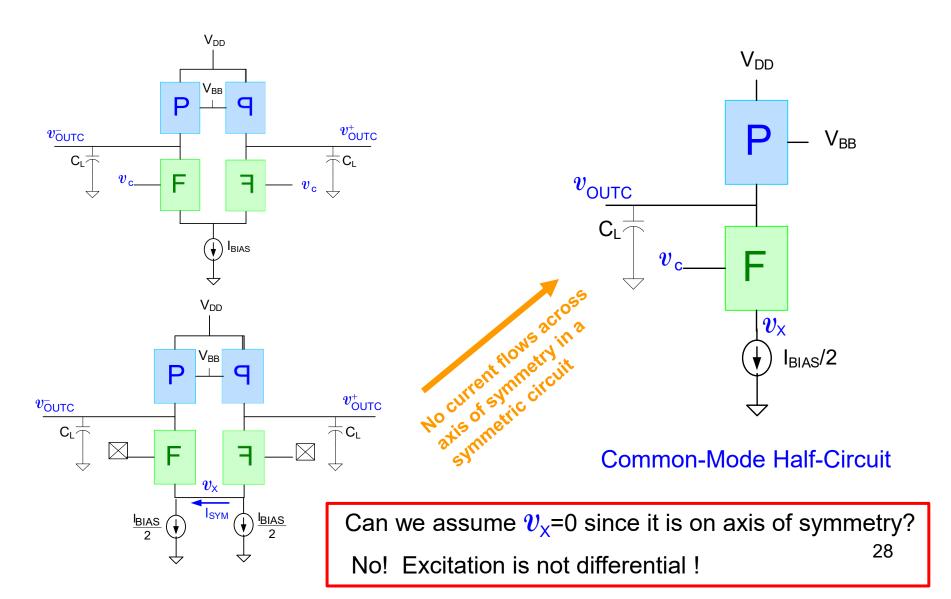

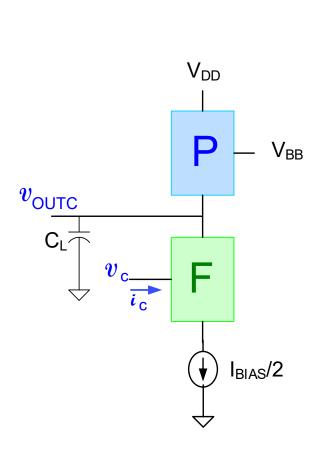

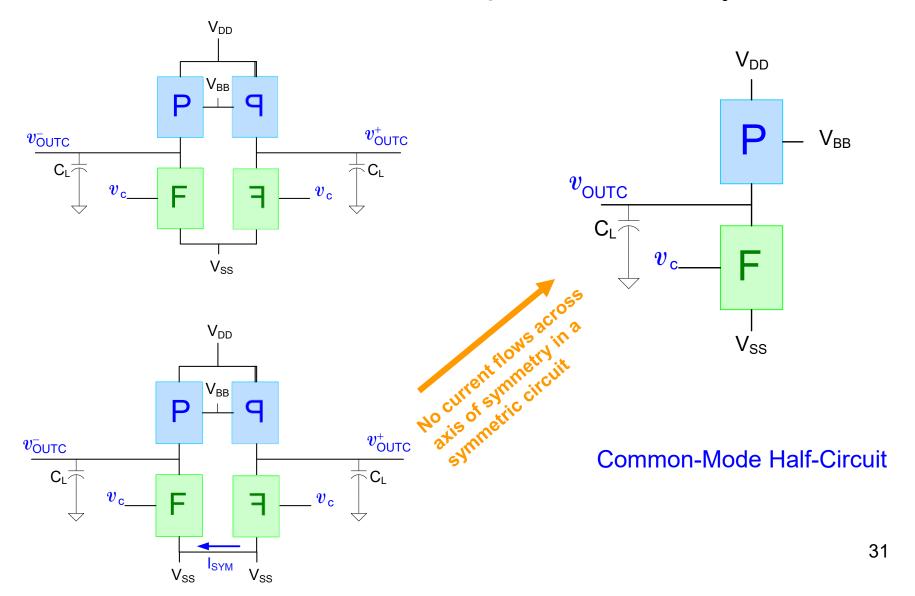

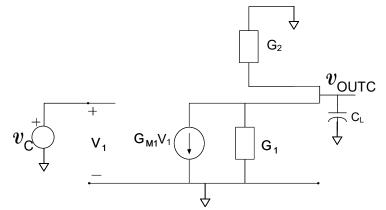

Consider tail-current bias amplifier

Consider tail-current bias amplifier with  $i_c$ =0

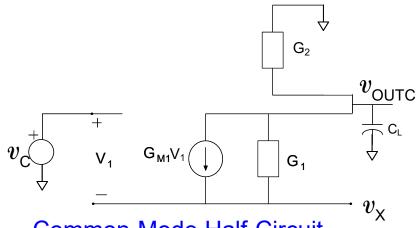

Common-Mode Half-Circuit (large signal: nonlinear)

Common-Mode Half-Circuit (small signal: linear)

$$\left. \begin{array}{l} v_{\mathrm{OUTC}}(\mathrm{sC+G_1+G_2}) + \mathrm{G_{M1}} v_1 = \mathrm{G_1} v_{\, \mathrm{X}} \\ v_{\, \mathrm{C}} = v_1 + v_{\, \mathrm{X}} \\ v_{\, \mathrm{X}} \mathrm{G_1} - \mathrm{G_{M1}} v_1 = v_{\, \mathrm{OUTC}} \, \mathrm{G_1} \end{array} \right\}$$

Solving, we obtain

$$v_{

m OUTC}$$

=0 thus A $_{

m C}$ =0

(Note: Have assumed an ideal tail current source in this analysis A<sub>C</sub> will be small but may not vanish if tail current source is not ideal. Analysis with nonideal current source is simple)

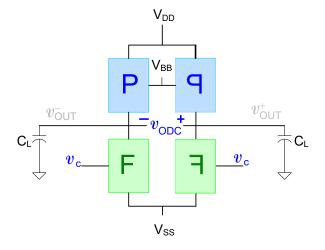

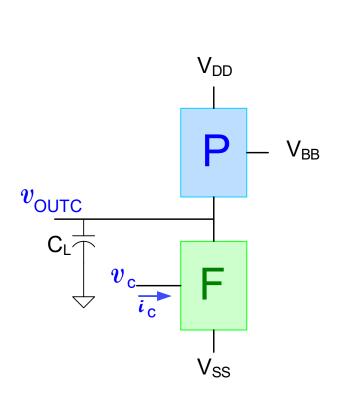

Consider tail-voltage bias amplifier with  $i_c$ =0

Consider tail-voltage bias amplifier with  $i_c$ =0

Common-Mode Half-Circuit (large signal: nonlinear)

Common-Mode Half-Circuit (small signal: linear)

$$v_{\text{OUTC}}(\text{sC+G}_1\text{+G}_2)\text{+G}_{\text{M1}}v_1 = 0$$

$v_{\text{C}} = v_1$

Solving, we obtain

$$\frac{v_{\text{OUTC}}}{v_{\text{C}}} = A_{\text{C}} = \frac{-G_{\text{M1}}}{\text{sC+G}_1 + G_2}$$

This circuit has a rather large common-mode gain and will not reject common-mode signals

- Not a very good <u>differential</u> amplifier

- But of no concern in applications where  $\,v_{\scriptscriptstyle

m C}$ =0

- Fully Differential Single-Stage Amplifier

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

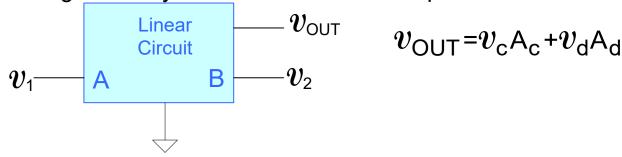

## **Overall Small-Signal Analysis**

As stated earlier, with common-mode gain and difference-mode gains available

$$v_{\text{OUT}} = v_{\text{c}} A_{\text{c}} + v_{\text{d}} A_{\text{d}}$$

- Fully Differential Single-Stage Amplifier

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

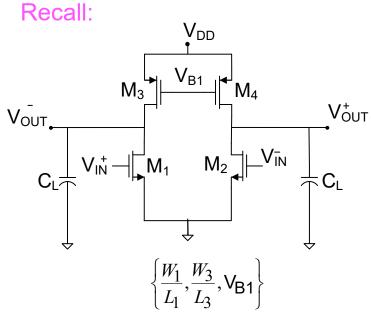

## Design of 5T op amp

# Single-stage low-gain differential op amp

#### **Quarter Circuit**

Single-Ended Output: Differential Input Gain

$$A(s) = \frac{-\frac{g_{m1}}{2}}{sC_{L} + g_{o1} + g_{o3}}$$

$$A_{o} = \frac{\frac{g_{m1}}{2}}{g_{o1} + g_{o3}}$$

$$GB = \frac{g_{m1}}{2C_{L}}$$

$$A(s) = \frac{-\frac{g_{m1}}{2}}{sC_{L} + g_{O1} + g_{O3}}$$

$$A_{o} = \frac{g_{m1}}{2} \\ g_{o1} + g_{o3}$$

$$GB = \frac{g_{_{m1}}}{2C_{_{L}}}$$

What are the number of degrees of freedom? (assume V<sub>DD</sub>, C<sub>I</sub> fixed, Symmetry)

Natural Parameters (assuming symmetry):

## Need a CMFB circuit to establish $V_{\rm B1}$

$$\left\{ \frac{W_1}{L_1}, \frac{W_3}{L_3}, \frac{W_5}{L_5}, V_{B1}, V_{B2} \right\}$$

Constraints:  $I_{D5} \simeq 2I_{D3}$

Net Degrees of Freedom: 4

- Expressions for A<sub>0</sub> and GB were obtained from quarter-circuit

- Expressions for A<sub>0</sub> and GB in terms of natural parameters for quarter circuit were messy

- Can show that expressions for A<sub>0</sub> and GB in terms of natural parameters for 5T amplifier are also messy

$$A(s) = \frac{-\frac{g_{m1}}{2}}{sC_{L} + g_{O1} + g_{O3}}$$

$$A_{o} = \frac{g_{m1}}{2} g_{o1} + g_{o3}$$

$$GB = \frac{g_{_{m1}}}{2C_{_{L}}}$$

What are the number of degrees of freedom? (assume V<sub>DD</sub>, C<sub>I</sub> fixed, Symmetry)

### Need a CMFB circuit to establish V<sub>B1</sub>

#### Natural Parameters:

$$\left\{ \frac{W_1}{L_1}, \frac{W_3}{L_3}, \frac{W_5}{L_5}, V_{\text{B1}}, V_{\text{B2}} \right\}$$

Constraints:  $I_{D5} \simeq 2I_{D3}$

$$I_{D5}{\simeq}2I_{D3}$$

Net Degrees of Freedom: 4

### **Practical Parameters:**

$$\left\{V_{EB1}, V_{EB3}, V_{EB5}, P\right\}$$

Will now express performance characteristics in terms of Practical Parameters 39

### **Quarter Circuit**

Single-Ended Output : Differential Input Gain

$$A(s) = \frac{-\frac{g_{m1}}{2}}{sC_{L} + g_{o1} + g_{o3}}$$

$$A_{o} = \frac{\frac{g_{m1}}{2}}{g_{o1} + g_{o3}}$$

$$GB = \frac{g_{m1}}{2C_{L}}$$

**Practical Parameters:**

$$\{V_{EB1}, V_{EB3}, V_{EB5}, P\}$$

$$A_{_{0}} = \left[\frac{1}{\lambda_{_{1}} + \lambda_{_{3}}}\right] \left(\frac{1}{V_{_{EB1}}}\right) \qquad GB = \left(\frac{P}{V_{_{DD}}C_{_{L}}}\right) \bullet \left[\frac{1}{2V_{_{EB1}}}\right]$$

Have 4 degrees of freedom but only two practical variables impact  $A_0$  and GB so still have 2 DOF after meet  $A_0$  and GB requirements

Need a CMFB circuit to establish V<sub>B1</sub>

Single-Ended Output: Differential Input Gain

Practical Parameters: {V<sub>EB1</sub>, V<sub>EB3</sub>, V<sub>EB5</sub>, P}

$$A_{0} = \left[\frac{1}{\lambda_{1} + \lambda_{3}}\right] \left(\frac{1}{V_{EB1}}\right) \qquad GB = \left(\frac{P}{V_{DD}C_{L}}\right) \bullet \left[\frac{1}{2V_{EB1}}\right]$$

$V_{OUT}$

{V<sub>EB3</sub>, V<sub>EB5</sub>, P}

{Ver1, Ver3, Vers

Design Strategy with fixed  $A_0$  and GB requirements:

- 1. Pick V<sub>FB1</sub> to meet gain requirements

- 2. Pick P to meet GB requirements

- 3. Pick  $V_{EB3}$  and  $V_{EB5}$  to achieve other desirable properties

(i.e. explore the remaining part of the design space)

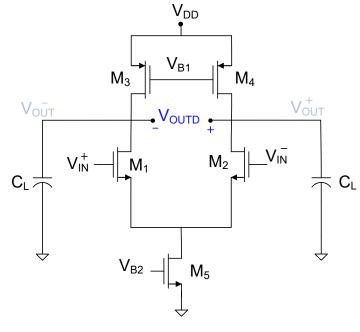

## Single-stage low-gain differential I/O op amp

## **Quarter Circuit**

$$\frac{\mathbf{V}_{\mathsf{OD}} = \mathbf{V}_{\mathsf{O}}^{\scriptscriptstyle{+}} - \mathbf{V}_{\mathsf{O}}^{\scriptscriptstyle{-}}}{}$$

### Differential Output : Differential Input Gain

$$A(s) = \frac{g_{m1}}{sC_{L} + g_{O1} + g_{O3}}$$

$$\mathsf{A}_{\scriptscriptstyle{\mathsf{o}}} = \frac{\mathsf{g}_{\scriptscriptstyle{\mathsf{m}1}}}{\mathsf{g}_{\scriptscriptstyle{\mathsf{o}1}} + \mathsf{g}_{\scriptscriptstyle{\mathsf{o}3}}}$$

$$\mathsf{GB} = \frac{\mathsf{g}_{\scriptscriptstyle \mathsf{m}}}{\mathsf{C}_{\scriptscriptstyle \mathsf{L}}}$$

$$A_{_{0}} = \left[\frac{1}{\lambda_{_{1}} + \lambda_{_{3}}}\right] \left(\frac{2}{V_{_{EB1}}}\right) \quad GB = \left(\frac{P}{V_{_{DD}}C_{_{L}}}\right) \bullet \left[\frac{1}{V_{_{EB1}}}\right]$$

Have 4 degrees of freedom but only two practical variables impact  $A_0$  and GB so still have 2 DOF after meet  $A_0$  and GB requirements that can be used for other purposes

## A<sub>D</sub> expressions valid for both tail-current and tail-voltage op amp

- Common-mode input range large for tail current bias

- Improved rejection of common-mode signals for tail current bias

- Two extra design degree of freedom for tail current bias

- Improved output signal swing for tail voltage bias (will show later)

- Fully Differential Single-Stage Amplifier

- General Differential Analysis

- 5T Op Amp from simple quarter circuit

- Biasing with CMFB circuit

- Common-mode and differential-mode analysis

- Common Mode Gain

- Overall Transfer Characteristics

- Design of 5T Op Amp

- Slew Rate

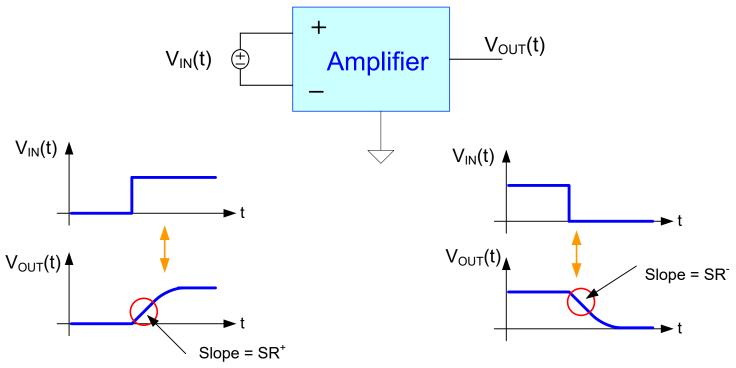

# Slew Rate

Definition: The slew rate of an amplifier is the maximum rate of change that can occur at the output node

- SR is a nonlinear large-signal characteristic

- Input is over-driven (some devices in amplifier usually leave normal operating region)

- Hard input overdrive depicted in this figure

- Magnitude of SR<sup>+</sup> and SR<sup>-</sup> usually same and called SR (else SR<sup>+</sup> and SR<sup>-</sup> must be given)

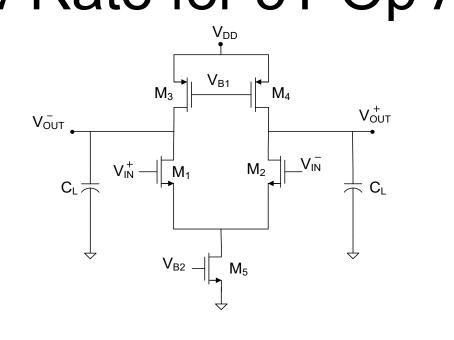

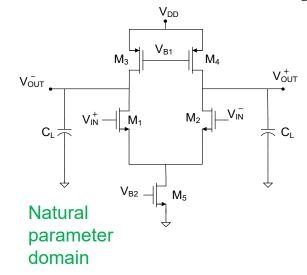

# Slew Rate for 5T Op Amp

With large step input on  $V_{IN}^+$ , all tail current ( $I_T$ ) will go to  $M_1$  thus turning off  $M_2$ thus current through  $M_4$  which is  $\frac{1}{2}$  of  $I_T$  will go to load capacitor  $C_1$

The I-V characteristics of any capacitor is

$$I=C\frac{dt}{dV}$$

Substituting  $I=I_T/2$ ,  $V=V_{OUT}^+$  and  $C=C_L$  obtain a voltage ramp at the output thus

$$SR^{+} = \frac{dV_{OUT}^{+}}{dt} = \frac{I_{T}}{2C_{L}} \quad \begin{array}{l} \text{Natural} \\ \text{parameter} \\ \text{domain} \end{array} \qquad SR^{+} = \frac{P}{V_{DD}2C_{L}} \quad \begin{array}{l} \text{Practical} \\ \text{parameter} \\ \text{domain} \end{array} \quad 47$$

$$SR^{+} = \begin{array}{c} P \\ V_{DD}2C_{L} \end{array}$$

Practical parameter domain

# Slew Rate for 5T Op Amp

$$SR^+ = \boxed{\frac{I_T}{2C_L}}$$

$$SR^{+} = \begin{array}{c} \\ \hline V_{DD}2C_{L} \end{array}$$

**Practical** parameter domain

Can SR<sup>+</sup> be expressed as product of model parameters and architecture dependent term?

$SR^{+} = \left[\frac{1}{2C_{I}}\right][I_{T}] \qquad SR^{+} = \left[\frac{1}{V_{DD} 2C_{I}}\right][P]$

Can SR+ be expressed in small-signal parameter domain? Question:

$$SR^{+} = \frac{g_{o1}I_{T}}{\lambda 2C_{I}} = \left| \frac{I_{T}}{\lambda 2C_{I}} \right| [g_{o1}]$$

# Slew Rate

It can be similarly shown that putting a large negative step on the input steer all current to M<sub>2</sub> thus the current to the capacitor C<sub>1</sub> will be I<sub>T</sub> minus the current from M<sub>2</sub> which is still  $I_T/2$ . This will cause a negative ramp voltage on  $V_{OUT}^+$  of value

$$SR^{-} = \frac{dV_{OUT}^{+}}{dt} = -\frac{I_{T}}{2C_{L}} = -\frac{P}{V_{DD}2C_{L}}$$

Since the magnitude of SR<sup>+</sup> and SR<sup>-</sup> are the same, obtain a single SR for the amplifier of value  $SR = \frac{P}{\sqrt{2} - 2C}$

# Interdependence of Parameters

$$A_{0} = \left[\frac{1}{\lambda_{1} + \lambda_{3}}\right] \left(\frac{1}{V_{EB1}}\right)$$

$$GB = \left(\frac{1}{2V_{DD}C_{L}}\right) \bullet \left[\frac{P}{V_{EB1}}\right]$$

$$SR = \frac{P}{V_{DD} 2C_L}$$

Note: With this structure, the three key performance characteristics {A<sub>0</sub>, GB, SR} can not be independently specified

e.g. If

$$V_{EB1}$$

is picked to set  $A_0$ , then  $\frac{P}{V_{DD}C_L}$  will determine both GB and SR

Alternately, observe

$$SR = \frac{GB}{A_0(\lambda_1 + \lambda_2)}$$

Stay Safe and Stay Healthy!

# End of Lecture 4